Name: \_\_\_\_\_

## Single Cycle Implementation Homework

Only problems 1 and 2 are due for credit.

- 1. Disassemble the following machine instructions:

- (a) **0x016a6020**

- (b) 0x014b6824

- (c) 0x35134321

- (d) 0x2000000

- (e) 0x000a5140

- (f) Ox11cfffa

- (g) 0x8e0b000c

- (h) **0x8e4efff8**

- (i) 0xae2d0010

- (j) 0x08100000

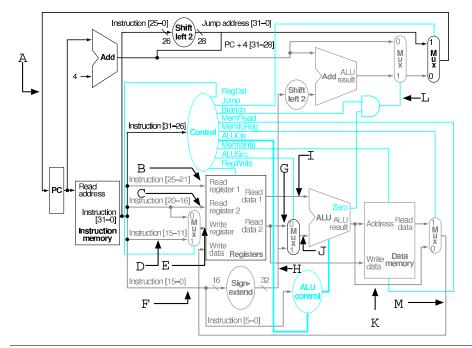

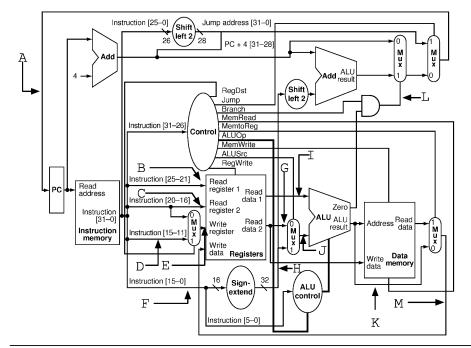

2. For each instruction below, determine the value at each of the labeled points in Figure 1. Assume that register x has the value 1000 \* x + 10 \* x. For example, assume \$0 is 0, \$1 is 1010, \$2 is 2020, \$31 is 31310, etc. In addition: Assume the current instruction is at address 0x0040001C, label fwd6 is 0x00400034, and bwd6 is 0x00400004. Represent the contents of memory location x as M[x]. Some values (e.g., the output of the ALU when doing a jump) are undefined. List all well-defined values — even if that value isn't used by the instruction.

| Point                                               | add \$12, \$3, \$2 | addi         | \$3, | \$2, | 131  | addi          | \$3, | \$2, | -16 | lw \$5 | 5, Ox | 5ABC(\$24) |

|-----------------------------------------------------|--------------------|--------------|------|------|------|---------------|------|------|-----|--------|-------|------------|

| А                                                   | 0x0040 0020        |              |      |      |      |               |      |      |     |        |       |            |

| В                                                   | 3                  |              |      |      |      |               |      |      |     |        |       |            |

| С                                                   | 2                  |              |      |      |      |               |      |      |     |        |       |            |

| D                                                   | 12                 |              |      |      |      |               |      |      |     |        |       |            |

| Е                                                   | 12                 |              |      |      |      |               |      |      |     |        |       |            |

| F                                                   | 24608 0x6020       |              |      |      |      |               |      |      |     |        |       |            |

| G                                                   | 2020 0x7E4         |              |      |      |      |               |      |      |     |        |       |            |

| Н                                                   | 0x00006020         |              |      |      |      |               |      |      |     |        |       |            |

| Ι                                                   | 3030 0xBD6         |              |      |      |      |               |      |      |     |        |       |            |

| J                                                   | 2020 7E4           |              |      |      |      |               |      |      |     |        |       |            |

| Κ                                                   | 5050 0x13BA        |              |      |      |      |               |      |      |     |        |       |            |

| L                                                   | 0                  |              |      |      |      |               |      |      |     |        |       |            |

| Μ                                                   | 5050 0x13BA        |              |      |      |      |               |      |      |     |        |       |            |

|                                                     |                    | 1            |      |      |      |               |      |      |     |        |       |            |

| Point                                               | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 6 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| Point                                               | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 3 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       | _          |

|                                                     | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 6 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       | _          |

| А                                                   | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | be   | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D                                    | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | ð be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E                               | sw \$4, -8(\$2) be | ∣<br>eq \$3, | \$2, | fwd6 | 6 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F                          | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 6 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G                     | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 6 be | <u>q</u> \$3, | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H                | sw \$4, -8(\$2) be | 1<br>eq \$3, | \$2, | fwd6 | 5 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I           | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 5 be | <u>q</u> \$3, | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J      | sw \$4, -8(\$2) be | 1<br>eq \$3, | \$2, | fwd6 | 5 be | q \$3,        | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J<br>K | sw \$4, -8(\$2) be | eq \$3,      | \$2, | fwd6 | 5 be | <u>q</u> \$3, | \$3, | bwd  | 6 j | fwd6   |       |            |

| A<br>B<br>C<br>D<br>E<br>F<br>G<br>H<br>I<br>J      | sw \$4, -8(\$2) be | 1<br>eq \$3, | \$2, | fwd6 | 5 be | <u>q</u> \$3, | \$3, | bwd  | 6 j | fwd6   |       |            |

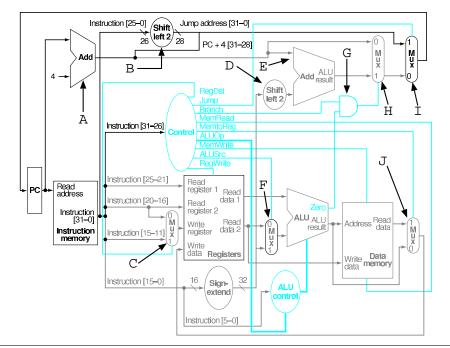

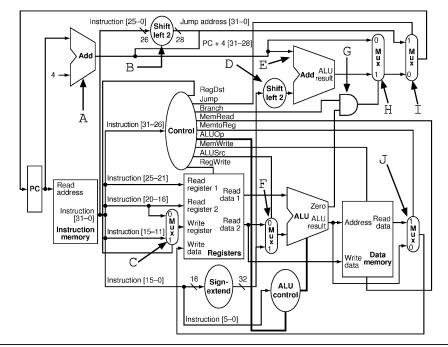

- 3. What is the purpose of the ALU labeled "A" in Figure 2?

- 4. Why does the input to the ALU labeled "A" in Figure 2 have the constant value 4?

- 5. What is the purpose of the "shift-left 2" labeled "B" in Figure 2?

- 6. Why are jump targets encoded as a word address instead of a byte address?

- 7. What is the purpose of the sign extender in Figure 2? Why is it necessary?

- 8. What is the purpose of the mux labeled "C" in Figure 2?

- 9. What is the purpose of the "shift-left 2" labeled "D"' in Figure 2?

- 10. What is the purpose of the mux labeled "F" in Figure 2?

- 11. What is the purpose of the and gate labeled "G" in Figure 2?

- 12. What is the collective purpose of the muxes labeled "H" and "I" in Figure 2?

- 13. Does it matter whether mux "H" comes first or mux "I"?

- 14. What is the purpose of the mux labeled "J" in Figure 2?

- 15. Add components to Figure 2 to show how to add a "branch if not equal" instruction to the single-cycle CPU.

Version: 2013:vgh66

FIGURE 4.24 The simple control and datapath are extended to handle the jump instruction. An additional multiplexor (at the upper right) is used to choose between the jump target and either the branch target or the sequential instruction following this one. This multiplexor is controlled by the jump control signal. The jump target address is obtained by shifting the lower 26 bits of the jump instruction left 2 bits, effectively adding 00 as the low-order bits, and then concatenating the upper 4 bits of PC+ 4 as the high-order bits, thus yielding a 32-bit address. Copyright © 2009 Elsevier, Inc. All rights reserved.

Figure 1: Single Cycle CPU with labeled points

FIGURE 4.24 The simple control and datapath are extended to handle the jump instruction. An additional multiplexor (at the upper right) is used to choose between the jump target and either the branch target or the sequential instruction following this one. This multiplexor is controlled by the jump control signal. The jump target address is obtained by shifting the lower 26 bits of the jump instruction left 2 bits, effectively adding 00 as the low-order bits, and then concatenating the upper 4 bits of PC+ 4 as the high-order bits, thus yielding a 32-bit address. Copyright © 2009 Elsevier, Inc. All rights reserved.

Figure 2: Single Cycle CPU with labeled parts

FIGURE 4.24 The simple control and datapath are extended to handle the jump instruction. An additional multiplexor (at the upper right) is used to choose between the jump target and either the branch target or the sequential instruction following this one. This multiplexor is controlled by the jump control signal. The jump target address is obtained by shifting the lower 26 bits of the jump instruction left 2 bits, effectively adding 00 as the low-order bits, and then concatenating the upper 4 bits of PC+ 4 as the high-order bits, thus yielding a 32-bit address. Copyright © 2009 Elsevier, Inc. All rights reserved.

Figure 3: Single Cycle CPU with labeled points (black & white)

FIGURE 4.24 The simple control and datapath are extended to handle the jump instruction. An additional multiplexor (at the upper right) is used to choose between the jump target and either the branch target or the sequential instruction following this one. This multiplexor is controlled by the jump control signal. The jump target address is obtained by shifting the lower 26 bits of the jump instruction left 2 bits, effectively adding 00 as the low-order bits, and then concatenating the upper 4 bits of PC+ 4 as the high-order bits, thus yielding a 32-bit address. Copyright © 2009 Elsevier, Inc. All rights reserved.

Figure 4: Single Cycle CPU with labeled parts (black & white)