Name:

## Design an Adder

Follow the steps below to design an unsigned adder.

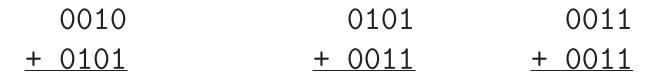

1. Complete the following addition problems directly in binary. In other words, work through the addition using the algorithm you learned in 1st grade. Don't convert them to base 10.

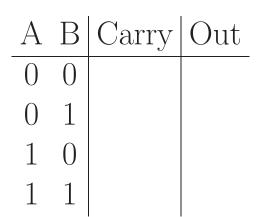

2. Complete the truth table below for a one-bit adder. (Notice how this circuit can also handle the right-most column of the above addition problems.)

3. Draw the circuit for this truth table.

The circuit you just designed and drew is called a "Half Adder"

Name: \_\_\_\_\_

4. Make a truth table for a circuit that can handle the 2nd column of the above addition problems. Hint: It should have three inputs and two outputs: (Don't forget to label the inputs and outputs.)

| 0 | 0 | 0 |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| 1 | 1 | 1 |

5. Draw the circuit for the above truth table. This circuit is called a "Full Adder"

Name: \_\_\_\_\_

6. Show how you can combine 4 full adders into a single device that can add two 4-bit numbers. (Just use a box with the inputs and outputs labeled to represent each full adder. You need not draw the gates inside each full adder.)

7. What is the big-O running time for your adder? Why? (If you are not familiar with big-O, then do this: Draw a graph with the number of input bits on the x-axis and time on the y-axis. What is the shape of your graph? Why?)

8. What is the big-O size of your adder? Why? (If you are not familiar with big-O, then do this: Draw a graph with the number input bits on the *x*-axis and the total number of gates on the *y*-axis. What is the shape of your graph? Why?)

Name: \_\_\_\_\_

Challenge questions:

9. Is the big-O of time necessarily the same as the big-O of size? Why or why not?

10. Design an adder that is faster.

11. Design an adder that is smaller.

12. When would you prefer a fast adder to a small adder? When would you prefer a small adder to a fast adder?